## Ultracompact, 1.5 A Thermoelectric Cooler (TEC) Controller

#### **GENERAL DESCRIPTION**

The SLM8833 is a monolithic TEC controller with an integrated TEC controller. It has a linear power stage and a pulse-width modulation (PWM) power stage. The linear controller works with the PWM driver to control the internal power MOSFETs in an H-bridge configuration. Depending on the control voltage at the CONT input, the SLM8833 drives current through a TEC to settle the temperature of a laser diode or a passive component attached to the TEC module to the programmed target temperature.

The control voltage applied to the CONT input pin is generated by a digital-to-analog converter (DAC) closing the digital proportional, integral, derivative (PID) loop of temperature control system.

The internal 2.50 V reference voltage provides a 1% accurate output that is used to bias a thermistor temperature sensing bridge as well as a voltage divider network to program the maximum TEC current and voltage limits for both the heating and cooling modes. It can also be a reference voltage for the DAC and the temperature sensing circuit, including a thermistor bridge and an analog-to-digital converter (ADC).

#### **FEATURES**

- Integrated super low R<sub>DSON</sub> MOSFETs for the TEC controller

- High efficiency single inductor architecture

- TEC voltage and current operation monitoring

- No external sense resistor required

- Independent TEC heating and cooling current limit settings

- Programmable maximum TEC voltage

- 2.0 MHz PWM driver switching frequency

- External synchronization

- 2.50 V reference output with 1% accuracy

- Digital thermal control loop compatible

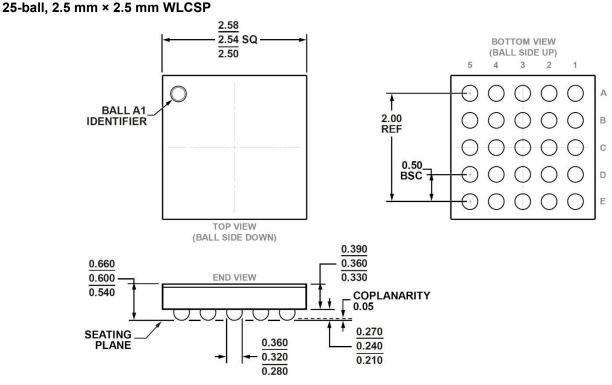

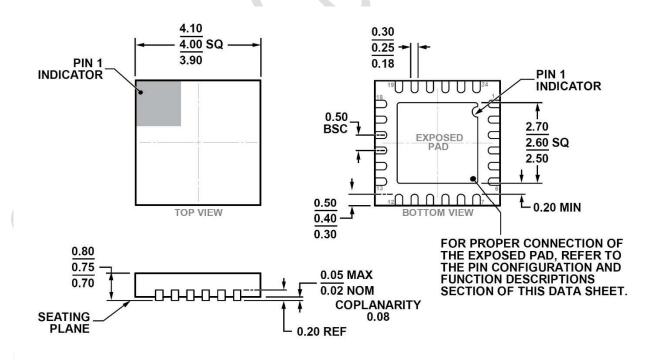

- Available in a 25-ball, 2.5 mm × 2.5 mm WLCSP or in a 24-lead, 4 mm × 4 mm QFN

#### **APPLICATIONS**

- TEC temperature control

- Optical modules

- Optical fiber amplifiers

- Optical networking systems

- Instruments requiring TEC temperature control

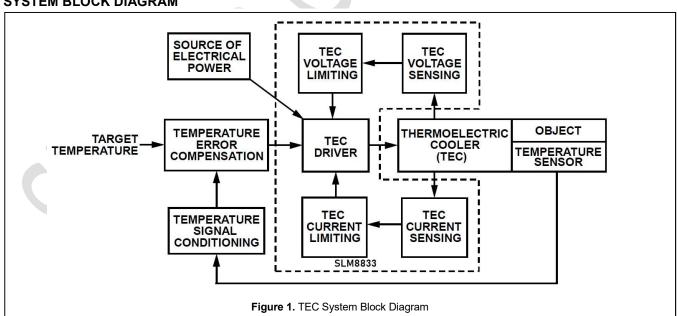

## SYSTEM BLOCK DIAGRAM

#### **TYPICAL APPLICATION CIRCUIT**

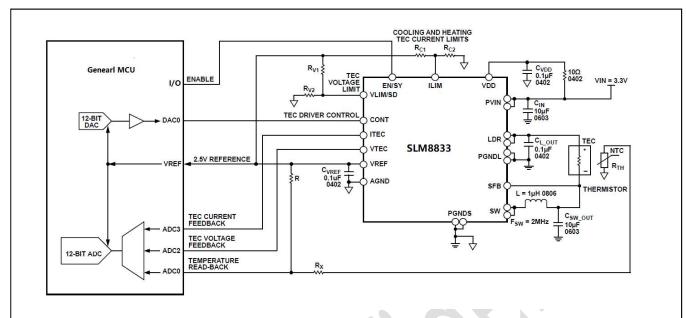

Figure 2. Typical Application Circuit with Digital PID Compensation in a Temperature Control Loop

Figure 3. TEC Controller in a Digital Temperature Control Loop (WLCSP)

## **PIN CONFIGURATION**

| Package                         | 25-ball, 2.5 mm × 2.5 mm WLCSP | 24-lead, 4 mm × 4 mm QFN |

|---------------------------------|--------------------------------|--------------------------|

| Pin Configuration<br>(Top View) | SLM8833                        | AGND 4 GND 7 T T DNC 1   |

#### **PIN DESCRIPTION**

| Pin No.                |                  | Din Nama    | Description                                                                                                                           |  |  |

|------------------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| WLCSP                  | QFN              | Pili Naille | Description                                                                                                                           |  |  |

| A1, A2                 | 18, 19           | PGNDL       | Power Ground of the Linear TEC Controller.                                                                                            |  |  |

| A3 to<br>A5, B3,<br>B4 | 1, 20<br>to 24   | DNC         | Do Not Connect. Don't connect to pins.                                                                                                |  |  |

| B1, B2                 | 17               | LDR         | Output of the Linear TEC Controller.                                                                                                  |  |  |

| B5                     | 3                | VLIM/SD     | Voltage Limit/Shutdown. This pin sets the cooling and heating TEC voltage limits. When this pin is pulled low, the device shuts down. |  |  |

| C1, C2                 | N/A <sup>1</sup> | PVIN        | Power Input for the TEC Controller.                                                                                                   |  |  |

| N/A <sup>1</sup>       | 16               | PVINL       | Power Input for the Linear TEC Driver.                                                                                                |  |  |

| N/A <sup>1</sup>       | 15               | PVINS       | Power Input for the PWM TEC Driver.                                                                                                   |  |  |

| C3                     | 11               | ITEC        | TEC Current Output.                                                                                                                   |  |  |

| C4                     | 2                | CONT        | Control Input of the TEC Driver. Apply a control signal from the DAC to this pin to close the thermal loop.                           |  |  |

| C5                     | 4                | ILIM        | Current Limit. This pin sets the TEC cooling and heating current limits.                                                              |  |  |

| D1, D2                 | 14               | SW          | Switch Node Output of the PWM TEC Controller.                                                                                         |  |  |

| D3                     | 9                | VTEC        | TEC Voltage Output.                                                                                                                   |  |  |

| D4                     | 8                | EN/SY       | Enable/Synchronization. Set this pin high to enable the device. An external synchronization clock input can be applied to this pin.   |  |  |

| D5                     | 5                | VDD         | Power for the Controller Circuits.                                                                                                    |  |  |

| E1, E2                 | 12, 13           | PGNDS       | Power Ground of the PWM TEC Controller.                                                                                               |  |  |

| E3                     | 10               | SFB         | Feedback of the PWM TEC Controller Output.                                                                                            |  |  |

| E4                     | 7                | AGND        | Signal Ground.                                                                                                                        |  |  |

| E5                     | 6                | VREF        | 2.5 V Reference Output.                                                                                                               |  |  |

| N/A <sup>1</sup>       | 0                | EPAD        | Exposed Pad. Solder to the analog ground plane on the board.                                                                          |  |  |

N/A1: Not Available.

## **ORDERING INFORMATION** Industrial Range: -40°C to +125°C

| Order Part No. | Package                        | QTY       |

|----------------|--------------------------------|-----------|

| SLM8833FA-7G   | 25-ball, 2.5 mm × 2.5 mm WLCSP | 500/Reel  |

| SLM8833EC      | 24-lead, 4 mm × 4 mm QFN       | 1000/Reel |

## **ABSOLUTE MAXIMUM RATINGS**

| PVIN to PGNDL / PGNDS (WLCSP)        |                                         |       | -0.3 V ~ 6.0 V              |

|--------------------------------------|-----------------------------------------|-------|-----------------------------|

| PVINL to PGNDL; PBINS to PGNDS (QFN) |                                         |       | -0.3 V ~ 6.0 V              |

| LDR to PGNDL (WL0                    | CSP)                                    |       | -0.3 V ~ V <sub>PVIN</sub>  |

| LDR to PGNDL (QFN                    | 1)                                      |       | -0.3 V ~ V <sub>PVINL</sub> |

| SW to PGNDS                          |                                         |       | -0.3 V ~ 6.0 V              |

| SFB / VLIM/SD / ILIM                 | // /CONT/ EN/SY to AGND                 |       | -0.3 V ~ V <sub>VDD</sub>   |

| AGND to PGNDL / P                    | GNDS                                    |       | -0.3 V ~ 0.3 V              |

| VDD / ITEC / VTEC t                  | o AGND                                  |       | -0.3 V ~ 6.0 V              |

| VREF to AGND                         |                                         |       | -0.3 V ~ 3 V                |

| Maximum Current                      |                                         |       |                             |

| VREF to AGND                         |                                         |       | 20 mA                       |

| ITEC to AGND                         |                                         |       | 50 mA                       |

| VTEC to AGND                         |                                         |       | 50 mA                       |

| Maximum junction te                  | mperature, T <sub>JMAX</sub>            |       | 150°C                       |

| Storage temperature                  | range, T <sub>STG</sub>                 |       | -65°~+150°C                 |

| Operating temperatu                  | re range, T」                            |       | -40°C~+125°C                |

|                                      | Junction to Ambient, R <sub>th-JA</sub> | WLCSP | 48 °C/w                     |

| Package Thermal                      | duriction to Ambient, Tur-5A            | QFN   | 37 °C/w                     |

| Resistance                           | Junction to Case, R <sub>th-JC</sub>    | WLCSP | 0.6 °C/w                    |

|                                      | QFN QFN                                 |       | 1.65 °C/w                   |

| ESD (HBM)                            |                                         |       | 2000 V                      |

| ESD (MM)                             |                                         |       | 200 V                       |

| ESD (FICDM)                          |                                         |       | 1500 V                      |

| Latch-up                             |                                         |       | +/- 100 mA                  |

|                                      |                                         |       |                             |

#### Note:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS (TBD)**

Test condition is  $V_{IN}$  = 2.7 V to 5.5 V,  $T_J$  = -40°C ~ +125°C for minimum/maximum specifications, and  $T_A$  = 25°C for typical specifications, unless otherwise specified.

| r typical spec              | cifications, unless otherwise specif   | fied.                                                |      |                             |           |      |

|-----------------------------|----------------------------------------|------------------------------------------------------|------|-----------------------------|-----------|------|

| Symbol                      | Parameter                              | Condition                                            | Min. | Тур.                        | Max.      | Unit |

| Power Supp                  | ply                                    |                                                      |      |                             |           |      |

| $V_{PVIN}$                  | Driver Supply Voltage                  |                                                      | 2.7  |                             | 5.5       | V    |

| $V_{VDD}$                   | Controller Supply Voltage              |                                                      | 2.7  |                             | 5.5       | V    |

| I <sub>VDD</sub>            | Supply Current                         | PWM switching                                        |      | 12                          |           | mA   |

| $I_{SD}$                    | Shutdown Current                       | EN/SY = AGND<br>or VLIM/SD = AGND                    |      | 350                         | 700       | μA   |

| UVLO                        | Under Voltage Lockout<br>Threshold     | V <sub>VDD</sub> Rising                              | 2.45 | 2.55                        | 2.65      | V    |

| OVLO                        | Under Voltage Lockout<br>Hysteresis    |                                                      | 80   | 90                          | 100       | mV   |

| Reference \                 | Voltage                                |                                                      |      |                             |           |      |

| $V_{VREF}$                  | Reference Voltage                      | I <sub>VREF</sub> = 0 mA to 10 mA                    | 2.47 | 2.50                        | 2.52<br>5 | V    |

| Linear Outp                 | out                                    |                                                      |      |                             |           |      |

| $V_{LDR}$                   | Output Voltage Low Output Voltage High | I <sub>LDR</sub> = 0 A                               |      | 0<br>V <sub>PVIN</sub>      |           | V    |

| 1                           | Maximum Source Current                 | $T_J = -40^{\circ}\text{C to } +105^{\circ}\text{C}$ | 1.5  |                             |           | A    |

| LDR_SOURCE                  |                                        | T <sub>J</sub> = -40°C to +125°C                     | 1.2  |                             |           |      |

| I <sub>LDR_</sub> SINK      | Maximum Sink Current                   | T <sub>J</sub> = -40°C to +105°C                     |      |                             | 1.5       | A    |

|                             |                                        | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |      |                             | 1.2       |      |

| _                           |                                        | WLCSP, V <sub>PVIN</sub> = 5.0 V                     |      | 28                          | 35        |      |

|                             | P-MOSFET ON Resistance                 | WLCSP, V <sub>PVIN</sub> = 3.3 V                     |      | 31                          | 38        | mΩ   |

| RDSON_PMOS                  | (I <sub>LDR</sub> = 0.6 A)             | QFN, V <sub>PVIN</sub> = 5.0 V                       |      | 50                          | 65        |      |

|                             |                                        | QFN, V <sub>PVIN</sub> = 3.3 V                       |      | 53                          | 70        |      |

|                             |                                        | WLCSP, V <sub>PVIN</sub> = 5.0 V                     |      | 21                          | 30        |      |

| D                           | N-MOSFET ON Resistance                 | WLCSP, V <sub>PVIN</sub> = 3.3 V                     |      | 23                          | 35        | mΩ   |

| RDSON_NMOS                  | $(I_{LDR} = 0.6 A)$                    | QFN, V <sub>PVIN</sub> = 5.0 V                       |      | 37                          | 55        |      |

|                             |                                        | QFN, V <sub>PVIN</sub> = 3.3 V                       |      | 40                          | 65        |      |

| ILDR_P_LKG                  | P-MOSFET Leakage Current               |                                                      |      | 0.1                         | 10        | μΑ   |

| I <sub>LDR_N_LKG</sub>      | N-MOSFET Leakage Current               |                                                      |      | 0.1                         | 10        | μA   |

| ALDR                        | Linear Amplifier Gain                  |                                                      |      | 40                          |           | V/V  |

| ILDR_SH_GNDL                | LDR Short-Circuit Threshold            | LDR short to PGNDL, enter hiccup                     |      | 2.2                         |           | Α    |

| I <sub>LDR_SH_PVIN(L)</sub> | LDR Short-Circuit Threshold            | LDR short to PVIN, enter hiccup                      |      | -2.2                        |           | Α    |

| THICCUP                     | Hiccup Cycle                           |                                                      |      | 15                          |           | ms   |

| PWM Outpu                   | ut                                     |                                                      |      |                             |           |      |

|                             | Output Voltage Low                     |                                                      |      | 0.06 x<br>V <sub>PVIN</sub> |           | .,   |

| $V_{SFB}$                   | Output Voltage High                    | Output Voltage High                                  |      | 0.93 x<br>V <sub>PVIN</sub> |           | V    |

| low oaves                   | Maximum Source Current                 | $T_J = -40^{\circ}\text{C to } +105^{\circ}\text{C}$ | 1.5  | 21 4114                     |           | Α    |

| Isw_source                  | waxiiiuiii Source Current              | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 1.2  |                             |           |      |

| 1.2 A<br>65 80 mg<br>80 95              |

|-----------------------------------------|

| 80 ms                                   |

| 80                                      |

|                                         |

| 95                                      |

|                                         |

| 60                                      |

| 65 ms                                   |

| 75                                      |

| 85                                      |

| 10 μ <i>A</i>                           |

| 10 μ <i>Α</i>                           |

| ns                                      |

| 93 %                                    |

| 2 µA                                    |

|                                         |

| 2.15 MF                                 |

| 0.8 V                                   |

| V                                       |

| 3.25 M⊢                                 |

| 90 %                                    |

| ns                                      |

| 10 Cy                                   |

| 0.5 μ <i>Α</i>                          |

| 0.5 μΑ                                  |

|                                         |

| / <sub>VREF</sub> V                     |

| 1.2 V                                   |

| 2.02 V                                  |

| 0.52 V                                  |

| +0.2 μ <i>Α</i>                         |

| 42.5 μ <i>Α</i>                         |

|                                         |

| m/                                      |

| m/                                      |

| ( ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( |

| V <sub>LIM</sub>                   | VLIM/SD Input Voltage Range     |                                                                                                                                                       | 0.2       |                | V <sub>VDD</sub> /2      | V   |

|------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|--------------------------|-----|

| IILIMC                             | VLIM/SD Input Current Cooling   | V <sub>OUT2</sub> < V <sub>VREF</sub> /2                                                                                                              | -0.2      |                | +0.2                     | μA  |

|                                    |                                 | Vout2 > VvREF/2, sinking                                                                                                                              |           | 10             |                          | •   |

| Ііцімн                             | VLIM/SD Input Current Heating   | current                                                                                                                                               | 8         | 10             | 12                       | μA  |

| TEC Curren                         | t Measurement (WLCSP)           |                                                                                                                                                       | ,         |                |                          |     |

| Rcs                                | Current Sense Gain              | V <sub>PVIN</sub> = 3.3 V                                                                                                                             |           | 0.52<br>5      |                          | V/A |

| 1403                               | Carrein Conico Cam              | V <sub>PVIN</sub> = 5 V                                                                                                                               |           | 0.52<br>5      |                          | V/A |

| I <sub>LDR_ERROR</sub>             | Current Measurement             | 700mA ≤ I <sub>LDR</sub> ≤ 1 A, V <sub>PVIN</sub> = 3.3 V                                                                                             | -10       |                | +10                      | %   |

|                                    | Accuracy                        | 800mA ≤ I <sub>LDR</sub> ≤ 1 A, V <sub>PVIN</sub> = 5 V                                                                                               | -10       |                | +10                      | %   |

| VITEC_@_700m                       |                                 | V <sub>PVIN</sub> = 3.3 V, cooling,<br>V <sub>VREF</sub> /2 + I <sub>LDR</sub> × R <sub>CS</sub>                                                      | 1.59<br>7 | 1.61<br>8      | 1.64<br>9                | V   |

| VITEC_@_<br>-700mA                 | ITEC Valtage Acquirect          | V <sub>PVIN</sub> = 3.3 V, heating,<br>V <sub>VREF</sub> /2 - I <sub>LDR</sub> × R <sub>CS</sub>                                                      | 0.84      | 0.88           | 0.89                     | V   |

| VITEC_@_800m                       | TTEC Voltage Accuracy           | V <sub>PVIN</sub> = 5 V, cooling, V <sub>VREF</sub> /2<br>+ I <sub>LDR</sub> × R <sub>CS</sub>                                                        | 1.65<br>7 | 1.67<br>8      | 1.71<br>8                | V   |

| VITEC_@_<br>-800mA                 |                                 | V <sub>PVIN</sub> = 5 V, heating, V <sub>VREF</sub> /2<br>- I <sub>LDR</sub> × R <sub>CS</sub>                                                        | 0.78      | 0.82<br>2      | 0.83<br>6                | V   |

| TEC Curren                         | t Measurement (QFN)             |                                                                                                                                                       |           |                |                          |     |

| Б                                  | Compant Samua Cain              | V <sub>PVIN</sub> = 3.3 V                                                                                                                             |           | 0.52<br>5      |                          | V/A |

| Rcs                                | Current Sense Gain              | V <sub>PVIN</sub> = 5 V                                                                                                                               |           | 0.52<br>5      |                          | V/A |

| I <sub>LDR_ERROR</sub>             | Current Measurement             | 700mA ≤ I <sub>LDR</sub> ≤ 1 A, V <sub>PVIN</sub> = 3.3 V                                                                                             | -15       |                | +15                      | %   |

| ILDR_ERROR                         | Accuracy                        | 800mA ≤ I <sub>LDR</sub> ≤ 1 A, V <sub>PVIN</sub> = 5 V                                                                                               | -15       |                | +15                      | %   |

| VITEC_@_700m                       |                                 | $V_{PVIN}$ = 3.3 V, cooling,<br>$V_{VREF}/2 + I_{LDR} \times R_{CS}$                                                                                  | 1.37<br>4 | 1.61<br>8      | 1.86<br>1                | V   |

| VITEC_@_                           |                                 | V <sub>PVIN</sub> = 3.3 V, heating,                                                                                                                   | 0.75      | 0.88           | 1.01                     | V   |

| -700mA<br>V <sub>ITEC_@_800m</sub> | ITEC Voltage Accuracy           | V <sub>VREF</sub> /2 - I <sub>LDR</sub> × R <sub>CS</sub> V <sub>PVIN</sub> = 5 V, cooling, V <sub>VREF</sub> /2 + I <sub>LDR</sub> × R <sub>CS</sub> | 1.41<br>9 | 3<br>1.67<br>8 | 5<br>1.92<br>1           | V   |

| VITEC_@_<br>-800mA                 |                                 | V <sub>PVIN</sub> = 5 V, heating, V <sub>VREF</sub> /2<br>- I <sub>LDR</sub> × R <sub>CS</sub>                                                        | 0.70      | 0.83           | 0.95<br>5                | V   |

| VITEC                              | ITEC Voltage Output Range       | I <sub>TEC</sub> = 0 A                                                                                                                                | 0         | -              | V <sub>VREF</sub> - 0.05 | V   |

| VITEC_BIAS                         | ITEC Bias Voltage               | I <sub>LDR</sub> = 0 A                                                                                                                                | 1.21<br>5 | 1.25<br>0      | 1.28<br>5                | V   |

| IITEC_Max                          | Maximum ITEC Output Current     |                                                                                                                                                       | -2        |                | +2                       | mA  |

| TEC Voltage                        | e Measurement                   |                                                                                                                                                       |           |                |                          |     |

| A <sub>VTEC</sub>                  | Voltage Sense Gain              |                                                                                                                                                       | 0.24      | 0.25           | 0.26                     | V/V |

| VVTEC_@_1_V                        | Voltage Measurement<br>Accuracy | V <sub>LDR</sub> - V <sub>SFB</sub> = 1 V, V <sub>VREF</sub> /2 +<br>A <sub>VTEC</sub> × (V <sub>LDR</sub> - V <sub>SFB</sub> )                       | 1.47<br>5 | 1.50<br>0      | 1.52<br>5                | V   |

| VVTEC                              | VTEC Output Voltage Range       | , , ,                                                                                                                                                 | 0.00<br>5 |                | 2.62<br>5                | V   |

| V <sub>VTEC_B</sub>                | VTEC Bias Voltage               | V <sub>LDR</sub> = V <sub>SFB</sub>                                                                                                                   | 1.22      | 1.25           | 1.27                     | V   |

| I <sub>VTEC_Max</sub>              | Maximum VTEC Output             |                                                                                                                                                       | -2        |                | +2                       | mA  |

| Internal Sof                       | t Start                         |                                                                                                                                                       |           |                |                          |     |

| t <sub>ss</sub>      | Soft Start Time             |  |  | 80  |      | ms |

|----------------------|-----------------------------|--|--|-----|------|----|

| VLIM/SD SH           | VLIM/SD SHUTDOWN            |  |  |     |      |    |

| VVLIM/SD_THL         | VLIM/SD Low Voltage         |  |  |     | 0.07 | V  |

| Thermal SH           | Thermal SHUTDOWN            |  |  |     |      |    |

| T <sub>SHDN_TH</sub> | Thermal Shutdown Threshold  |  |  | 170 |      | Ĵ  |

| Tshdn_hys            | Thermal Shutdown Hysteresis |  |  | 17  |      | °C |

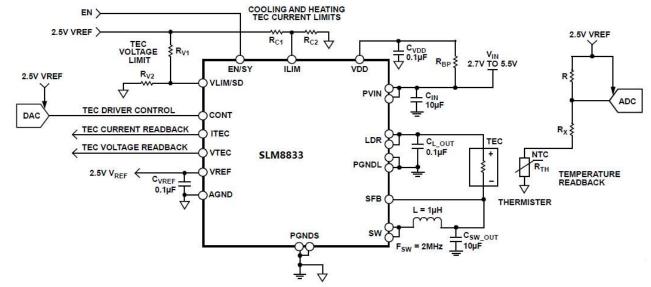

#### **TYPICAL OPERATING CHARACTERISTICS**

$T_A = 25$ °C, unless otherwise specified.

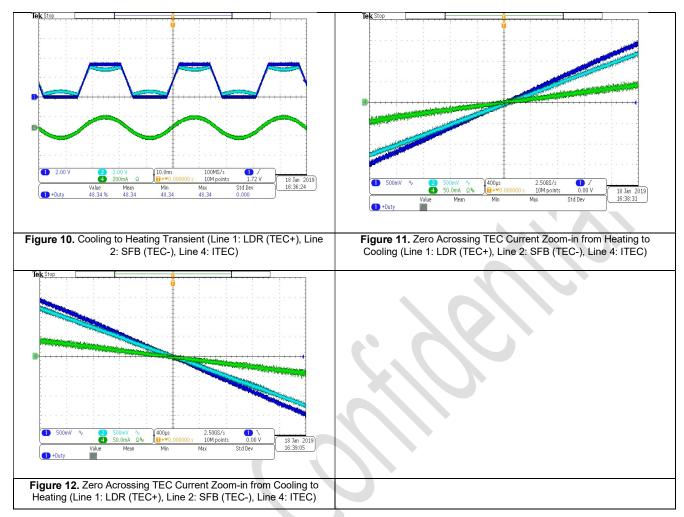

#### APPLICATION INFORMATION & WAVEFORMS

The SLM8833 is a single chip TEC controller that sets and stabilizes a TEC temperature. A control voltage from a DAC applied to the CONT input pin of the SLM8833 corresponds to the temperature setpoint of the target object attached to the TEC. . The SLM8833 controls an internal FET H-bridge whereby the direction of the current fed through the TEC can be either positive (for cooling mode), to pump heat away from the object attached to the TEC, or negative (for heating mode), to pump heat into the object attached to the TEC. Temperature is measured with a thermal sensor attached to the target object and the sensed temperature (voltage) is fed back to an ADC to complete a closed digital thermal control loop of the TEC. For the best overall stability, couple the thermal sensor close to the TEC. In most laser diode modules, a TEC and a NTC thermistor are already mounted in the same package to regulate the laser diode temperature. The TEC is differentially driven in an H-bridge configuration. The SLM8833 drives its internal MOSFET transistors to provide the TEC current. To provide good power efficiency and zero crossing quality, only one side of the H-bridge uses a PWM driver. Only one inductor and one capacitor are required to filter out the switching frequency. The other side of the H-bridge uses a linear output without requiring any additional circuitry. This proprietary configuration allows the SLM8833 to provide efficiency of >90%. For most applications, a 1 μH inductor, a 10 μF capacitor, and a switching frequency of 2 MHz maintain less than 1% of the worst-case output voltage ripple across a TEC.

The maximum voltage across the TEC and the current flowing through the TEC are set by using the VLIM/SD and ILIM pins. The maximum cooling and heating currents can be set independently to allow asymmetric heating and cooling limits. For additional details, see the Maximum TEC Voltage Limit section and the Maximum TEC Current Limit section.

#### **DIGITAL PID CONTROL**

The SLM8833 is used in a software controlled PID loop. An amplifier conditions the signal from the thermistor and connects to an external temperature measurement ADC. The signal from an external DAC that controls the temperature setpoint is applied to the CONT input pin.

#### **POWERING THE CONTROLLER**

The SLM8833 operates at an input voltage range of 2.7 V to 5.5 V that is applied to the VDD pin and the PVIN pin for the WLCSP (the PVINS pin and PVINL pin for the LFCSP. The VDD pin is the input power

for the driver and internal reference. The PVIN input power pins are combined for both the linear and the switching driver. Apply the same input voltage to all power input pins: VDD and PVIN. In some circumstances, an RC lowpass filter can be added optionally between the PVIN for the WLCSP (PVINS and PVINL for the LFCSP) and VDD pins to prevent high frequency noise from entering VDD, as shown in Figure 3. The capacitor and resistor values are typically 10  $\Omega$  and 100 nF, respectively. When configuring power supply to the SLM8833, keep in mind that at high current loads, the input voltage may drop substantially due to a voltage drop on the wires between the front-end power supply and the PVIN for the WLCSP (PVINS and PVINL for the LFCSP) pin. Leave a proper voltage margin when designing the front-end power supply to maintain the performance. Minimize the trace length from the power supply to the PVIN for the WLCSP (PVINS and PVINL for the LFCSP) pin to help mitigate the voltage drop. The features internal automatic overvoltage protection, when output voltage is higher than 115%.

#### **ENABLE AND SHUTDOWN**

To enable the SLM8833, apply a logic high voltage to the EN/SY pin while the voltage at the VLIM/SD pin is above the maximum shutdown threshold of 0.07 V. If either the EN/SY pin voltage is set to logic low or the VLIM/SD voltage is below 0.07 V, the controller goes into an ultralow current state. The current drawn in shutdown mode is 350 µA typically. Most of the current is consumed by the VREF circuit block, which is always on even when the device is disabled or shut down. The device can also be enabled when an external synchronization clock signal is applied to the EN/SY pin, and the voltage at VLIM/SD input is above 0.07 V. Table 6 shows the combinations of the two input signals that are required to enable the SLM8833.

| EN/SY Input            | VLIM/SD Input          | Controller |

|------------------------|------------------------|------------|

| >2.1 V                 | >0.07 V                | Enabled    |

| Switching between      | >0.07 V                | Enabled    |

| high >2.1 V and        |                        |            |

| low < 0.8 V            |                        |            |

| <0.8 V                 | No effect <sup>1</sup> | Shutdown   |

| Floating               | No effect <sup>1</sup> | Shutdown   |

| No effect <sup>1</sup> | ≤0.07 V                | Shutdown   |

<sup>&</sup>lt;sup>1</sup>No effect means this signal has no effect in shutting down or in enabling the device.

#### **OSCILLATOR CLOCK FREQUENCY**

The SLM8834 has an internal oscillator that generates a 2.0 MHz switching frequency for the PWM output stage. This oscillator is active when the enabled voltage at the EN/SY pin is set to a logic

level higher than 2.1 V and the VLIM/SD pin voltage is greater than the shutdown threshold of 0.07 V.

#### **External Clock Operation**

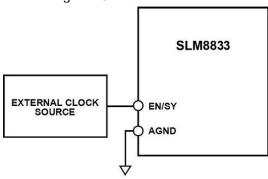

The PWM switching frequency of the SLM883 can be synchronized to an external clock from 1.85 MHz to 3.25 MHz, applied to the EN/SY input pin as shown on Figure 13.

Figure 13. Synchronize to an External Clock

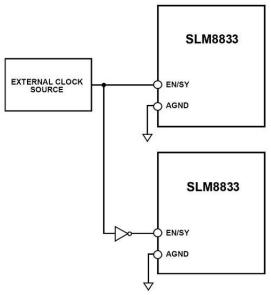

#### **Connecting Multiple SLM8833 Devices**

Multiple SLM883 devices can be driven from a single master clock signal by connecting the external clock source to the EN/SY pin of each slave device. The input ripple can be greatly reduced by operating the SLM8834 devices 180° out of phase from each other by placing an inverter at one of the EN/SY pins as shown in Figure 14.

Figure 14. Multiple SLM8833 Devices Driven from a Master Clock

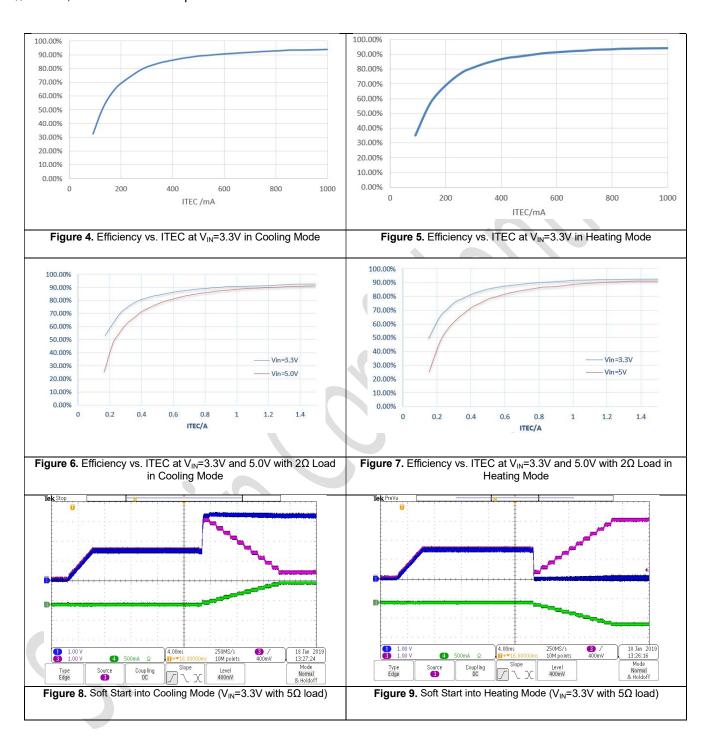

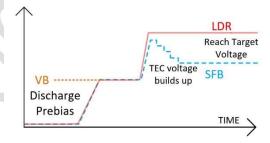

#### SOFT START ON POWER-UP

The SLM8833 has an internal soft start circuit that

generates aramp with a typical 150 ms profile to minimize inrush current during power-up. The settling time and the final voltage across the TEC depends on the TEC voltage required by the control voltage of voltage loop. The higher the TEC voltage is, the longer it requires to be built up. When the SLM8833 is first powered up, the linear

side discharges the output of any prebias voltage. As soon as the prebias is eliminated, the soft start cycle begins. During the soft start cycle, both the PWM and linear outputs track the internal soft start ramp until they reach midscale, where the control voltage, V<sub>C</sub>, is equal to the bias voltage, V<sub>B</sub>. From the midscale voltage, the PWM and linear outputs are then controlled by Vc and diverge from each other until the required differential voltage is developed across the TEC or the differential voltage reaches the voltage limit. The voltage developed across the TEC depends on the control point at that moment in time. Figure 15 shows an example of the soft start in cooling mode. Note that, as both the LDR and SFB voltages increase with the soft start ramp and approach V<sub>B</sub>, the ramp slows down to avoid possible current overshoot at the point where the TEC voltage starts to build up.

Figure 15. Soft Start Profile in Cooling Mode

## **TEC VOLTAGE/CURRENT MONITOR**

The TEC real-time voltage and current are detectable at VTEC and ITEC, respectively.

#### **Voltage Monitor**

VTEC is an analog voltage output pin with a voltage proportional to the actual voltage across the TEC. A center VTEC voltage of 1.25 V corresponds to 0 V across the TEC. Convert the voltage at VTEC and the voltage across the TEC using the following equation:

$$V_{VTEC} = 1.25 V + 0.25 \times (V_{LDR} - V_{SFB})$$

#### **Current Monitor**

ITEC is an analog voltage output pin with a voltage proportional to the actual current through the TEC. A center ITEC voltage of 1.25 V corresponds to 0 A through the TEC. Convert the voltage at ITEC and

the current through the TEC using the following equations:

$V_{ITEC\_COOLING} = 1.25 \text{ V} + I_{LDR} \times R_{CS}$ where the current sense gain (R<sub>CS</sub>) is 0.525 V/A.  $V_{ITEC\_HEATING} = 1.25 \text{ V} - I_{LDR} \times R_{CS}$

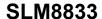

#### MAXIMUM TEC VOLTAGE LIMIT

The maximum TEC voltage is set by applying a voltage divider at the VLIM/SD pin to protect the TEC. The voltage limiter operates bidirectionally and allows the cooling limit to be different from the heating limit.

# Using a Resistor Divider to Set the TEC Voltage Limit

Separate voltage limits are set using a resistor divider. The internal current sink circuitry connected to VLIM/SD draws a current when the SLM8833 drives the TEC in a heating direction, which lowers the voltage at VLIM/SD. The current sink is not active when the TEC is driven in a cooling direction; therefore, the TEC heating voltage limit is always lower than the cooling voltage limit.

Figure 16. Using a Resistor Divider to Set the TEC Voltage Limit

Calculate the cooling and heating limits using the following equations:

$V_{VLIM\_COOLING} = V_{REF} \times R_{V2}/(R_{V1} + R_{V2})$ where  $V_{REF} = 2.5 \text{ V}$ .

$V_{VLIM\_HEATING} = V_{VLIM\_COOLING} - I_{SINK\_VLIM} \times R_{V1} / / R_{V2}$  where Isink vLIM = 10  $\mu$ A.

$V_{TEC\_MAX\_COOLING} = V_{VLIM\_COOLING} \times A_{VLIM}$

where  $A_{VLIM} = 2 \text{ V/V}$ .  $V_{TEC\_MAX\_HEATING} = V_{VLIM\_HEATING} \times A_{VLIM}$

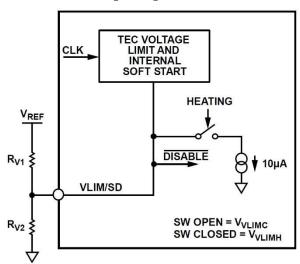

## MAXIMUM TEC CURRENT LIMIT

To protect the TEC, separate maximum TEC current

limits in cooling and heating directions are set by applying a voltage combination at the ILIM pin.

# Using a Resistor Divider to Set the TEC Current Limit

The internal current sink circuitry connected to ILIM draws a 40  $\mu$ A current when the SLM8833 drives the TEC in a cooling direction, which allows a high cooling current. Use the following equations to calculate the maximum TEC currents:

$V_{ILIM\_HEATING} = V_{REF} \times R_{C2}/(R_{C1} + R_{C2})$

where  $V_{REF} = 2.5 \text{ V}$ .

$V_{ILIM\_COOLING} = V_{ILIM\_HEATING} + I_{SINK\_ILIM} \times R_{C1} || R_{C2}$  where  $I_{SINK\_ILIM} = 40 \ \mu A$ .

where Isink\_ILIM = 40 µA.

$$I_{TEC\_MAX\_COOLING} = \frac{V_{ILIM\_COOLING} - 1.25 \text{ V}}{R_{CS}}$$

where  $R_{CS} = 0.525 \text{ V/A}$ .

$$I_{TEC\_MAX\_HEATING} = \frac{1.25 \text{ V} - V_{ILIM\_HEATING}}{R_{CS}}$$

VILIM\_HEATING must not exceed 1.2 V and VILIM\_COOLING must be more than 1.3 V to leave proper margins between the heating and the cooling modes.

Figure 17. Using a Resistor Divider to Set the TEC Current Limit

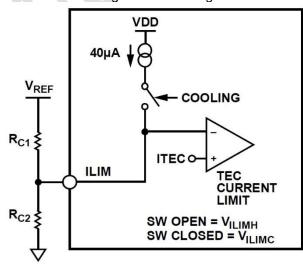

## **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                           | Pb-Free Assembly                 |

|-------------------------------------------------------------------------------------------|----------------------------------|

| Preheat & Soak Temperature min (Tsmin) Temperature max (Tsmax) Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |

| Average ramp-up rate (Tsmax to Tp)                                                        | 3°C/second max.                  |

| Liquidous temperature (TL) Time at liquidous (tL)                                         | 217°C<br>60-150 seconds          |

| Peak package body temperature (Tp)*                                                       | Max 260°C                        |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                   | Max 30 seconds                   |

| Average ramp-down rate (Tp to Tsmax)                                                      | 6°C/second max.                  |

| Time 25°C to peak temperature                                                             | 8 minutes max.                   |

Figure 18. Classification Profile

## PACKAGE INFORMATION

## 24-lead, 4 mm × 4 mm QFN

COMPLIANT TO JEDEC STANDARDS MO-220-WGGD-8.

## **Revision History**

Note: page numbers for previous revisions may differ from page numbers in current version

| Page or Item                | Subjects (major changes since previous revision) |  |  |

|-----------------------------|--------------------------------------------------|--|--|

| Rev 0.2 datasheet, 2019-9-3 |                                                  |  |  |

| Whole document              | New company logo released                        |  |  |

| Page 1                      | Remove "Rev0.1 January 2019"                     |  |  |